Block Diagram of India’s first Microprocessor -Shakthi from IIT Madras

Overview

1.In-order 3 stage 32/64 bit microcontroller supporting a subset of RISC-V ISA.

2.Low area and power consumption – operational frequency of < 200MHz on silicon.

3.Optimized variants for FPGA based soft-cores.

4.AXI4/AXI4-Lite/TileLink peripherals supported

5.Positioned against ARM’s M class cores

1.In-order 3 stage 32/64 bit microcontroller supporting a subset of RISC-V ISA.

2.Low area and power consumption – operational frequency of < 200MHz on silicon.

3.Optimized variants for FPGA based soft-cores.

4.AXI4/AXI4-Lite/TileLink peripherals supported

5.Positioned against ARM’s M class cores

Basic Specifications

1.Open source IP supporting RV32/64 – IMAC.

2.Optional Direct-mapped caches for instruction and data.

3.Supports Machine and User-modes only.

4.User-mode trap handling is optional.

5.Push button flow to generate variants and subsets of ISA.

6.Optimized sequential Multiplier and Divider for ASICs and FPGAs

7.OpenOCD based SoC debug support through JTAG.

8.OS Ports: FreeRTOS, Zephyr.

1.Open source IP supporting RV32/64 – IMAC.

2.Optional Direct-mapped caches for instruction and data.

3.Supports Machine and User-modes only.

4.User-mode trap handling is optional.

5.Push button flow to generate variants and subsets of ISA.

6.Optimized sequential Multiplier and Divider for ASICs and FPGAs

7.OpenOCD based SoC debug support through JTAG.

8.OS Ports: FreeRTOS, Zephyr.

FPGA Results

This implementation has also been burnt on FPGA’s and it consumes less than 3K LUT’s on a 7-series Xilinx FPGA.

This implementation has also been burnt on FPGA’s and it consumes less than 3K LUT’s on a 7-series Xilinx FPGA.

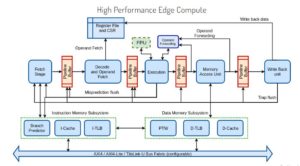

Shakti C-Class Processor-High Performance Edge Compute

Overview

An in-order 5-stage 64-bit microcontroller supporting the entire stable RISC-V ISA.

Targets mid-range compute systems: 200-800MHz (can be customized for 2 Ghz applications)

Supports RISC-V Linux, secure L4

Variants for low-power and high-performance.

Positioned against ARM’s Cortex A35/A55.

Basic Specifications

Supports RISC-V ISA: RV64IMAFD.

Compatible with latest privilege spec (v1.10) of RISC-V ISA and supports the sv39/48 virtualization scheme.

Single and Double Precision Floating point units compliant with IEEE-754.

Supports the OpenOCD based debug environment through JTAG.

Includes a High performance branch predictor with a Return-Address-Stack.

Caches: 16-64KB non-blocking pipelined Instruction and Data caches. Optional L2.

Includes operand forwarding scheme for better performance.

Boots RISC-V Linux.

Supports RISC-V ISA: RV64IMAFD.

Compatible with latest privilege spec (v1.10) of RISC-V ISA and supports the sv39/48 virtualization scheme.

Single and Double Precision Floating point units compliant with IEEE-754.

Supports the OpenOCD based debug environment through JTAG.

Includes a High performance branch predictor with a Return-Address-Stack.

Caches: 16-64KB non-blocking pipelined Instruction and Data caches. Optional L2.

Includes operand forwarding scheme for better performance.

Boots RISC-V Linux.

Physical Tapeout

We have successfully taped out a 22nm chip using this design which boots RISC-V Linux. It consumes 90-110 mW power on 22nm and requires about 175k gates for realization.

We have successfully taped out a 22nm chip using this design which boots RISC-V Linux. It consumes 90-110 mW power on 22nm and requires about 175k gates for realization.

FPGA Results

This implementation has also been burnt on FPGA’s and it consumes about 20K LUT’s on a 7-series Xilinx FPGA and reports DMIPS/MHz of 1.68

This implementation has also been burnt on FPGA’s and it consumes about 20K LUT’s on a 7-series Xilinx FPGA and reports DMIPS/MHz of 1.68

Comments